You are here: Foswiki>Timing Web>TimingSystemDocumentation>TimingSystemDocuments>TimingSystemEtherbone (08 Oct 2022, DietrichBeck)Edit Attach

Etherbone

Introduction

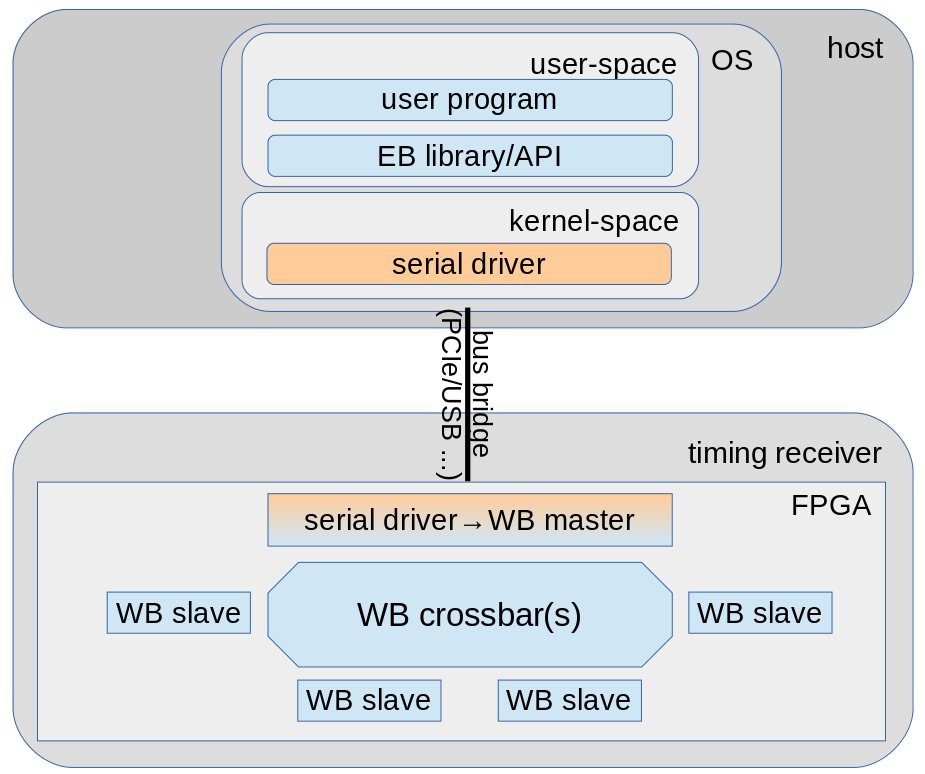

The idea behind the EtherBone (EB) protocol is to extend the reach of the embedded Wishbone (WB) V4 System-on-a-chip (SoC) bus system to remote field-programmable gate arrays or processors. The EtherBone core implementation connects a Wishbone bus via (typically) serial protocols such as Gigabit Ethernet, PCIe or USB to remote peripheral devices. EB acts as a transparent interconnect module towards attached WB Bus devices. EB was developed in the scope of the White Rabbit Timing Project at CERN and GSI/FAIR. White Rabbit will make use of EB as a means to issue commands to its timing nodes and control connected accelerator hardware. Figure: Stack from a userland application on a host to a Wishbone device in the FPGA including EtherBone.

As shown in the figure above, Etherbone can be used via almost any serial protocol available. Examples are PCIe, USB, UDP and TCP; even parallel buses like PCI or VME are possible using dedicated drivers. NB: The WB architecture employed by White Rabbit nodes at CERN and GSI, makes use of the so-called Self-Describing Bus (SDB) that allows to enumerate the cores that are live in the current FPGA binary. Etherbone and SDB allow to inspect and communicate with Wishbone devices in the FPGA.

Figure: Stack from a userland application on a host to a Wishbone device in the FPGA including EtherBone.

As shown in the figure above, Etherbone can be used via almost any serial protocol available. Examples are PCIe, USB, UDP and TCP; even parallel buses like PCI or VME are possible using dedicated drivers. NB: The WB architecture employed by White Rabbit nodes at CERN and GSI, makes use of the so-called Self-Describing Bus (SDB) that allows to enumerate the cores that are live in the current FPGA binary. Etherbone and SDB allow to inspect and communicate with Wishbone devices in the FPGA.

Further Details and Documentation

The best starting point is a Physical Review Special Topics edition, see here.Command Line Tools

To get familiar with using Etherbone, try out the so-called EB tools that are available at the command line of a Timing Receivers host system.Code Examples

- C API is available here

- a documented example is available here

- have a look at the so-called "EB Tools" that are part of our current release.

Docs

-- DietrichBeck - 17 November 2018| I | Attachment | Action | Size | Date | Who | Comment |

|---|---|---|---|---|---|---|

| |

etherboneStack.jpg | manage | 92 K | 17 Nov 2018 - 16:52 | DietrichBeck | etherbone stack |

Edit | Attach | Print version | History: r4 < r3 < r2 < r1 | Backlinks | View wiki text | Edit wiki text | More topic actions

Topic revision: r4 - 08 Oct 2022, DietrichBeck

Copyright © by the contributing authors. All material on this collaboration platform is the property of the contributing authors.

Copyright © by the contributing authors. All material on this collaboration platform is the property of the contributing authors. Ideas, requests, problems regarding Foswiki? Send feedback